Hello! now About Us

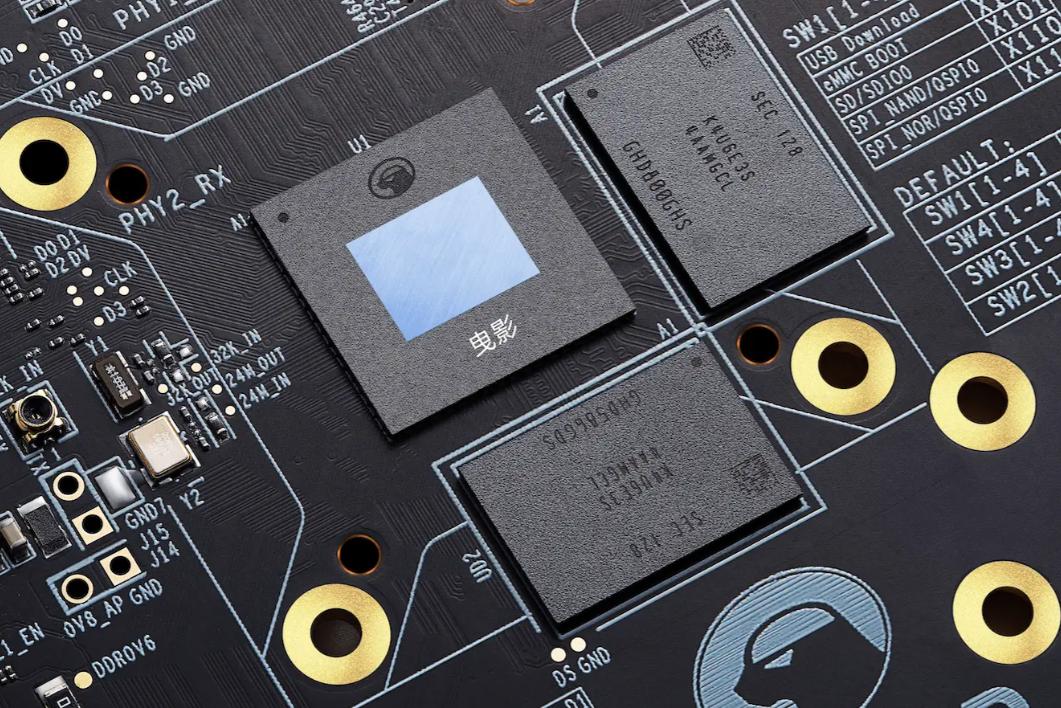

Working Principle of SoC System-on-Chip XCZU3EG-1SBVA484: A Comprehensive Analysis

7/15/2025 2:49:05 AM

In the era of rapid advancement in integrated circuit technology, System-on-Chip (SoC) has emerged as the cornerstone of intelligent terminals, industrial control systems, and communication networks, thanks to its high integration, low power consumption, and superior performance. The XCZU3EG-1SBVA484, a flagship product in Xilinx's Zynq UltraScale+ MPSoC series, exemplifies this trend by integrating processor cores, programmable logic, interface controllers, and system-level optimizations into a single chip. This article delves into its technical essence from four perspectives: architectural design, core module collaboration, bus communication mechanisms, and typical application scenarios.

1. Heterogeneous Computing Architecture: Dual-Engine System Operation

The XCZU3EG-1SBVA484 adopts a heterogeneous computing architecture combining dual-core Arm Cortex-A53 (APU) and dual-core Arm Cortex-R5F (RPU), achieving a balance between performance and power efficiency through functional specialization. The APU, operating at up to 1.5GHz, runs Linux-based operating systems and handles complex algorithms such as image processing and machine learning inference. In contrast, the RPU provides deterministic low-latency execution for time-critical tasks like sensor data acquisition and motor control.

Consider an industrial robotics application: the APU executes path planning algorithms while the RPU monitors motor encoder signals in real time, directly driving servo systems through hardware acceleration units (e.g., PWM controllers). This division of labor eliminates performance degradation from context switching in single-processor systems, boosting overall efficiency by over 30%.

2. Programmable Logic Layer: The Customizable Acceleration Engine

The integrated FPGA logic units represent the product's key differentiator from traditional SoCs. With approximately 154K logic cells (LUTs) and 352 DSP48E1 hard cores, the XCZU3EG-1SBVA484 enables users to design custom hardware accelerators using HDL languages like Verilog/VHDL. For instance, in 5G base stations, programmable logic can implement FFT/IFFT operations for baseband processing, achieving 10x performance improvement over software implementations while reducing power consumption by 60%.

Xilinx's Vivado Design Suite provides a complete toolchain for hardware development, covering IP core integration (e.g., DDR4 controllers, PCIe interfaces) to timing constraint optimization through graphical interfaces. Notably, the product supports partial reconfiguration (PR) technology, allowing dynamic updates of specific logic functions during runtime-a valuable feature for IoT gateways requiring flexible protocol adaptation.

3. Bus Architecture and Memory System: The Data Superhighway

The XCZU3EG-1SBVA484 employs a three-tier bus architecture:

AXI4 High-Speed Bus: Connects APU/RPU with DDR4 memory controllers, supporting 512-bit data paths and 25.6GB/s bandwidth for 4K video streaming and other data-intensive tasks.

AXI4-Lite Low-Speed Bus: Manages peripheral interfaces like UART and SPI through register-based control signal transmission.

Custom Bus Matrix: Enables direct interconnectivity between FPGA logic and processor cores, eliminating traditional bus bottlenecks.

The memory system adopts a hierarchical design:

L1/L2 Caches: The A53 cores feature 32KB L1 instruction/data caches and 1MB L2 cache, significantly reducing memory access latency.

DDR4 Controller: Supports dual-channel 3200MT/s operation with expandable capacity up to 8GB.

QSPI Flash: Stores boot code and fixed configuration parameters for rapid system initialization.

4. Typical Application Scenarios: From Edge Computing to Industrial IoT

Smart Cameras: The APU runs facial recognition algorithms, the RPU processes infrared sensor data, and FPGA logic implements H.265 video encoding. This tri-engine collaboration enables 4K@30fps real-time processing at just 1W power consumption.

Industrial HMI: FPGA-based multi-protocol conversion (e.g., Modbus to Profinet) replaces traditional PLC+IPC architectures, while the RPU handles touchscreen inputs and the APU runs HMI configuration software.

Autonomous Driving Domain Controller: FPGA accelerates LiDAR point cloud preprocessing, the APU executes SLAM algorithms, and the R5F monitors vehicle status-all communicating with the main ECU via PCIe Gen3 interfaces.

5. Technological Evolution: From Single Chips to System-Level Innovation

The XCZU3EG-1SBVA484 embodies three key trends in SoC development:

Heterogeneous Integration: Chiplet technology combines 16nm FinFET processors with 28nm FPGA logic in a single package, optimizing performance-cost tradeoffs.

Software-Hardware Co-Design: Xilinx's Vitis unified software platform streamlines algorithm development to hardware acceleration, enabling performance gains without deep hardware expertise.

Enhanced Security: Integrated TrustZone technology provides hardware-based isolation for critical data, meeting functional safety (ISO 26262) and cybersecurity requirements in Industry 4.0 applications.

Conclusion

The working principle of the XCZU3EG-1SBVA484 reveals the core logic of modern SoC design: achieving full-stack functionality-from sensor interfaces to complex algorithms-within a single chip through heterogeneous computing, programmable logic, and system-level optimization. As AIoT and autonomous driving markets explode, such "software-defined hardware" systems are becoming critical infrastructure for industrial transformation. Looking ahead, breakthroughs in 3D packaging and compute-in-memory technologies promise to push SoC capabilities beyond traditional Moore's Law limitations, ushering in a new era of innovation.

Fudong Communication (Shenzhen) Group Co., Ltd., established in 2004, is a specialized global first tier semiconductor agent/distributor.

Fudong Mall is an online e-commerce platform belonging to Fudong Communication (Shenzhen) Group Co., Ltd. Fudong collaborates with global electronic component distributors and Chinese spot inventory suppliers.